AMBA BUS

AMBA

: Advanced Microcontroller Bus Architecture

Decoder와 Multiplexer를 이용하여 Memory Map 만든다.

Master가 1개로, Master과 Slave 1이 통신하면 나머지 Slave가 통신을 못하는 경우가 발생한다.

Master가 모든 정보를 Slave들에게 보낸다. ( AXI와 반대되는 부분 )

AMBA Interface

- AHB : Advanced High - performance Bus

- 고성능 : 고속 데이터 전송을 지원하며, 높은 대역폭을 제공한다.

- 멀티마스터 아키텍쳐 : 여러 마스터 장치(CPU, DMA)가 버스를 공유할 수 있다.

- AHB 구조

- Master : 버스를 제어하고 데이터를 전송하는 장치 (CPU, DMA)

- Slave : 마스터의 명령을 받아 데이터를 전송하거나 수신하는 장치 (메모리, 주변 장치 등)

- Arbiter : 멀티마스터 호나경에서 버스 사용을 조정하는 장치.

- Decoder : 주소에 따라 올바른 슬레이브를 선택하는 장치.

- APB : Advanced Peripheral Bus

- 저속, 저전력 : 낮은 전력 소모와 단순한 인터페이스를 제공하며, 고성능이 필요 없는 주변 장치에 적합한다.

- 단순한 프로토콜 : 데이터 전송 과정이 단순하여 구현이 용이하다.

- APB 구조

- Master : Bridge 역할. AHB와 같은 고속 버스로부터 명령을 받아 APB로 전달.

- Slave : APB 버스에 연결된 주변 장치들 (타이머, UART 등)

Bridge 왼쪽이 AHB, Bridge 오른쪽이 APB이다.

AMBA1 ~ AMBA5까지 있다.

- AXI-Lite : Burst 기능이 없다. 메모리 시작주소, 크기 신호가 없다.

- Burst : 데이터 버스에서 연속된 데이터 블록을 효율적으로 전송하는 방식이다. (메모리 시작 주소 & 크기 입력)

- 대용량의 데이터를 처리할 때, 단일 주소 접근으로 여러 데이터 항목을 연속적으로 전송할 수 있음. → 전송 효율 크게 향상.

- AXI4-Stream : 단방향 전송 Bus이다. Master → Slave로만 보낸다. ( Read X, Write 0 )

Master가 여러 개이므로 Master1이 Slave1과 통신을 하고 있을 때 Master2가 나머지 Slave 중 한 개와 통신할 수 있다.

Master가 Slave1과 통신할 때 나머지 Slave가 Master에게 정보를 주지 않는다.

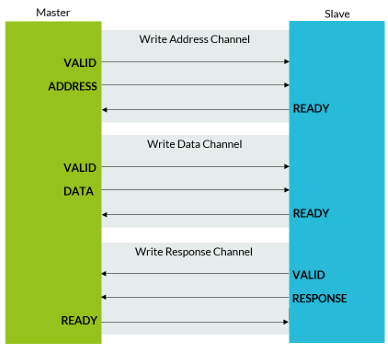

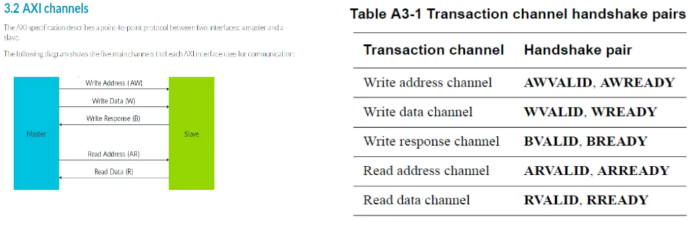

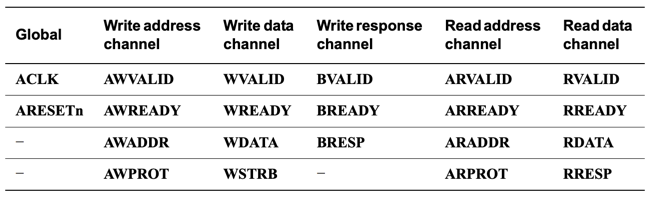

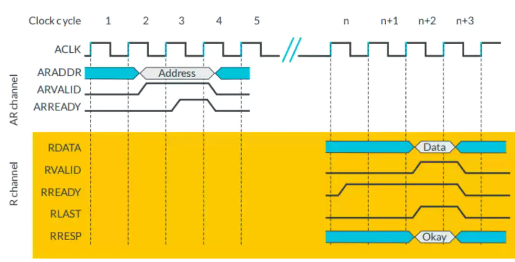

AW, W, B, AR, R이 각각 하나의 채널이다.

AW, W, B를 묶어서 Write Transaction, AR, R을 묶어서 Read Transaction이라고 한다.

Write Channel이 3개, Read Channel이 2개 있다.

AXI 4 protocol, interface이라고 한다.

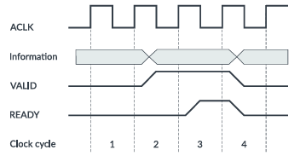

VALID, READY, Handshake가 나온다. 모든 채널이 같은 handshake 방식을 가진다.

- VALID : Source에서 Destination으로 가는 신호.

- 어떤 정보를 요구할 때 무조건 VALID 신호가 포함되어있어야 한다.

- READY : Destination에서 Source로 가는 신호.

- 해당 정보를 받아들이고 처리할 때 무조건 READY 신호가 포함되어있어야 한다.

- HANDSHAKE : : VALID와 READY 신호가 모두 1일 때 해당 CHANNEL의 정보 처리가 끝난 것이다.

- HADNSHAKE가 성립되면 VALID, READY 신호 모두 비활성화.

이 신호는 address, response 값 등 여러 개가 될 수 있다.

Master에서 Slave에게 Address 정보를 요구할 수 있다. ( Read Address 채널이 생김. )

Slave가 Master에게 해당 주소에 있는 정보를 보낼 수 있다. ( Read Data 채널이 생김. )

read transction 처리 부분과 write transaction 처리 부분과 독립되어 있어 서로 영향을 주지 않는다.

정보를 보내는 순서

- Addr, Data, Response 정보를 보내는 순간 VLAID 신호를 High로 한다.

- Slave에서 Addr 정보를 latch, 저장을 하면 READY 신호를 보낸다.

- Master에서 clk이 posedge 되면 READY 신호를 받아들인다.

- READY 신호를 받아들이면 VALID를 0으로 한다.

READY 신호가 VALID 신호보다 먼저 On을 한다. 받을 준비가 되어있다는 표시다.

빠른 정보 처리를 위해 하는 방식이다.

ex) CPU에서 Addr을 보내면서 READY 신호를 보낸다.

VALID와 READY 신호가 동시에 들어오는 형태이다.

- Write address channel - AWVALID AWREADY / AWADDR : 쓰기 주소

- Write data channel - WVALID WREADY / WDATA : 쓰기 주소에 해당하는 데이터

- Write response channel - BVALID BREADY / BREAD : 쓰기 응답

- Read address channel - ARVALID ARREADY / ARADDR : 읽기 주소

- Read data channel - RVALID RREADY / RDATA : 읽기 주소에 해당하는 데이터

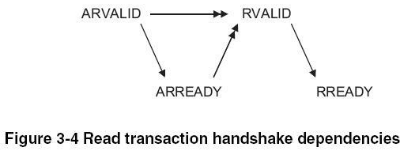

Read transactio handshake dependencies

RDATA를 전송할려면 ARVALID, ARREADY가 asserted 되어야만 한다.

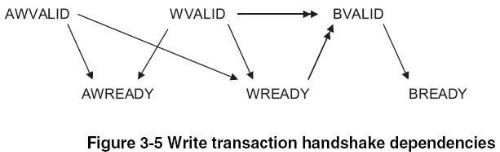

Write transaction handshake dependencies

BVALID : response 정보는 WVALID와 WREADY가 asserted 된 후 전송해야 한다.

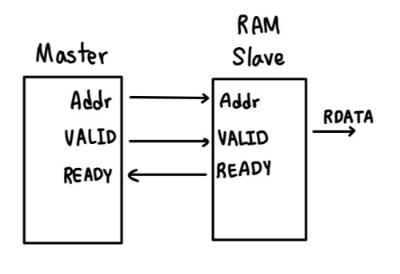

AXI4 - Lite : Single Master, Burst 기능이 없다.

- Master가 Addr을 보내 읽을 데이터의 주소를 Slave로 보낸다.

- Slave는 Addr을 받아들이고 Data를 준비한다.

- Slave가 Data를 준비하고, RREADY 신호를 1로 설정하여 Master가 데이터를 읽을 준비가 되었음을 알린다.

- Master는 Slave가 RREADY 신호를 1로 설정했는 것을 확인하면, 데이터를 수신한다.

master.sv

`timescale 1ns / 1ps

module AXI_Master (

// Global Signal

input logic ACLK,

input logic ARESETn,

// READ ADDRESS CHANNEL

input logic ARREADY,

output logic ARVALID,

output logic [31:0] ARADDR,

// READ DATA CHANNEL

output logic RREADY,

input logic RVALID,

input logic [31:0] RDATA,

// Sending inputs data to transfered through AXI protocol

input logic [31:0] araddr,

input logic arvalid,

output logic [ 7:0] rdata

);

////// READ ADDR CHANNEL MASTER

enum {

AR_IDLE_S,

AR_VALID_S

}

ar_state, ar_state_next;

always_ff @(posedge ACLK, negedge ARESETn) begin

if (!ARESETn) ar_state <= AR_IDLE_S;

else ar_state <= ar_state_next;

end

// Next State Logic

always_comb begin : AR_NEXT_STATE

ar_state_next = ar_state;

case (ar_state)

AR_IDLE_S: begin

if (arvalid) ar_state_next = AR_VALID_S;

end

AR_VALID_S: begin

if (ARVALID && ARREADY) ar_state_next = AR_IDLE_S;

end

endcase

end

// Output logic

always_comb begin

case (ar_state)

AR_IDLE_S: begin

ARVALID = 1'b0;

end

AR_VALID_S: begin

ARVALID = 1'b1;

ARADDR = araddr;

end

default: ARVALID = 1'b0;

endcase

end

///////////////// READ DATA CHANNEL MASTER

enum {

R_IDLE_S,

R_READY_S,

R_VALID_S

}

r_state, r_state_next;

always_ff @(posedge ACLK, negedge ARESETn) begin

if (!ARESETn) r_state <= R_IDLE_S;

else r_state <= r_state_next;

end

// Next State Logic

always_comb begin : R_NEXT_STATE

r_state_next = r_state;

case (r_state)

R_IDLE_S: if (ARREADY) r_state_next = R_READY_S;

R_READY_S: if (RVALID) r_state_next = R_IDLE_S;

//R_VALID_S: r_state_next = R_IDLE_S;

endcase

end

// Output logic

always_comb begin

case (r_state)

R_IDLE_S: begin

RREADY = 1'b0;

end

R_READY_S: begin

RREADY = 1'b1;

rdata = RDATA;

end

default: RREADY = 1'b0;

endcase

end

endmodule

slave.sv

`timescale 1ns / 1ps

module AXI_Slave (

// Global Signal

input logic ACLK,

input logic ARESETn,

// READ ADDRESS CHANNEL

output logic ARREADY,

input logic ARVALID,

input logic [31:0] ARADDR,

// READ DATA CHANNEL

input logic RREADY,

output logic RVALID,

output logic [31:0] RDATA

// output memory data

//output logic [ 7:0] rdata

);

logic [7:0] slave_mem[0:7];

logic [7:0] araddr;

initial begin

for (int i = 0; i < 8; i++) slave_mem[i] = 100 + i;

end

///////// READ ADDR CHANNEL SLAVE

enum {

AR_IDLE_S,

AR_READY_S

}

ar_state, ar_state_next;

//

always_ff @(posedge ACLK, negedge ARESETn) begin

if (!ARESETn) ar_state <= AR_IDLE_S;

else ar_state <= ar_state_next;

end

// Next State Logic

always_comb begin

ar_state_next = ar_state;

case (ar_state)

AR_IDLE_S: if (ARVALID) ar_state_next = AR_READY_S;

AR_READY_S: if (ARVALID && ARREADY) ar_state_next = AR_IDLE_S;

endcase

end

// output Logic

always_comb begin

case (ar_state)

AR_IDLE_S: ARREADY = 1'b0;

AR_READY_S: begin

ARREADY = 1'b1;

araddr = ARADDR;

end

default: ARREADY = 1'b0;

endcase

end

//assign rdata = slave_mem[araddr];

//////////// READ DATA CHANNEL SLAVE

enum {

R_IDLE_S,

R_VALID_S

}

r_state, r_state_next;

//

always_ff @(posedge ACLK, negedge ARESETn) begin

if (!ARESETn) r_state <= R_IDLE_S;

else r_state <= r_state_next;

end

// Next State Logic

always_comb begin

r_state_next = r_state;

case (r_state)

R_IDLE_S: if (RREADY) r_state_next = R_VALID_S;

R_VALID_S: if (RVALID && RREADY) r_state_next = R_IDLE_S;

endcase

end

// output Logic

always_comb begin

case (r_state)

R_IDLE_S: RVALID = 1'b0;

R_VALID_S: begin

RVALID = 1'b1;

RDATA = slave_mem[araddr];

end

default: RVALID = 1'b0;

endcase

end

endmodule

top.sv

`timescale 1ns / 1ps

module top (

input logic ACLK,

input logic ARESETn,

input logic [31:0] araddr,

input logic arvalid,

output logic [ 7:0] rdata

);

logic ARREADY;

logic ARVALID;

logic [31:0] ARADDR;

logic RREADY;

logic RVALID;

logic [31:0] RDATA;

AXI_Master U_Master (.*);

AXI_Slave U_Slave_Memory (.*);

endmodule

tb_axi_mem.sv

`timescale 1ns / 1ps

module tb_axi_mem ();

logic ACLK;

logic ARESETn;

// READ ADDR CHANNEL

logic [31:0] araddr;

logic arvalid;

logic [ 7:0] rdata;

top dut (.*);

always #5 ACLK = ~ACLK;

initial begin

ACLK = 1'b0;

ARESETn = 1'b0;

#10 ARESETn = 1'b1;

#10;

repeat(3) @(posedge ACLK); araddr = 8'd1; arvalid = 1'b1;

repeat(1) @(posedge ACLK); arvalid = 1'b0;

repeat(3) @(posedge ACLK); araddr = 8'd3; arvalid = 1'b1;

repeat(1) @(posedge ACLK); arvalid = 1'b0;

repeat(3) @(posedge ACLK); araddr = 8'd6; arvalid = 1'b1;

repeat(1) @(posedge ACLK); arvalid = 1'b0;

repeat(3) @(posedge ACLK); araddr = 8'd7; arvalid = 1'b1;

repeat(1) @(posedge ACLK); arvalid = 1'b0;

#20 $finish;

end

endmodule

schematic

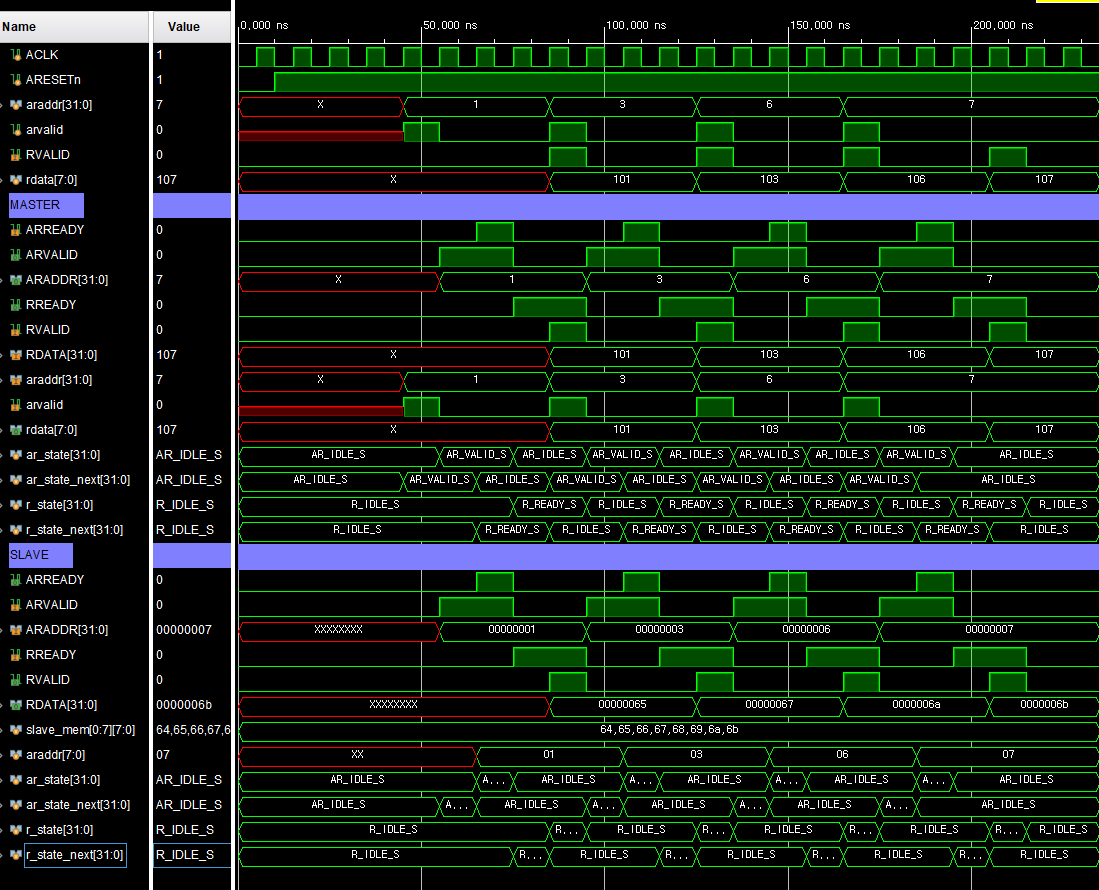

simulation

- Addr을 Master에게 보내면 ARVALID를 Slave로 보낸다.

- Slave에서 ARVALID 신호를 받으면 ADDR을 저장해놓고 ARREADY을 MASTER로 보낸다.

- MASTER에서 ARREADY를 받으면 RREADY를 Slave로 보낸다.

- SLAVE에서 RREADY를 받으면 RVALID & RDATA를 MASTER에게 보낸다.

- MASTER에서 RVALID & RDATA를 받으면 RDATA를 내보내고 RREADY를 0으로 한다.

// MASTER : ARVALID, RREADY를 제어함.

// SLAVE : ARREADY, RVALID를 제어함.

- MASTER에서 ADDRESS를 주면서 정보를 요구함.

- SLAVE에서 ADDRESSS를 받으면서 정보 보낼 준비 완료 신호 보냄.

- MASTER에서 정보 받을 준비 완료 신호 보냄.

- SLAVE에서 정보를 보내줌.

AMBA_AXI pdf :

https://s3.techne-atelier.com/files/digital-design/axi4/102202_0100_01_Introduction_to_AMBA_AXI.pdf

AMBA_AXI4 pdf

'[하만]세미콘 아카데미 > verilog' 카테고리의 다른 글

| 0618 UVM (0) | 2024.07.10 |

|---|---|

| 0617 AXI_memory (0) | 2024.07.10 |

| 0604 RISC-v GPO GPI GPIO (0) | 2024.07.10 |

| 0603 RISC-v GPI GPO (0) | 2024.07.09 |

| 0530~0531 RISCV_Type (0) | 2024.07.09 |