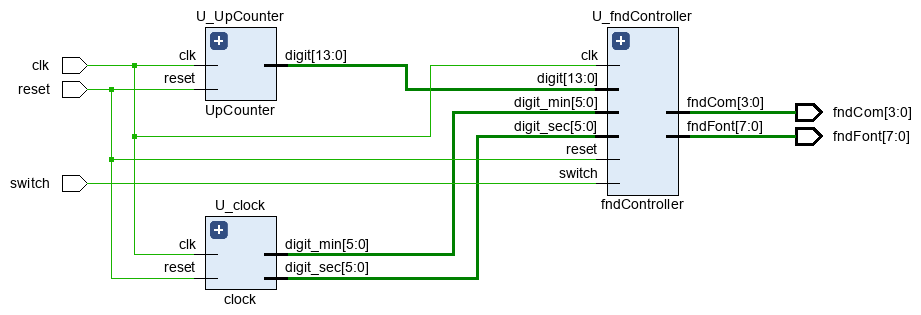

clock_upCounter

: clock 과 upCounter를 switch로 조종하여 FND에 표시한다.

clock_upCounter.v

`timescale 1ns / 1ps

module clock_upCounter(

input clk,

input reset,

input switch,

output [7:0] fndFont,

output [ 3:0] fndCom

);

wire [7:0] fndFont_clock, fndFont_upCounter;

wire [5:0] digit_sec, digit_min;

wire [13:0] digit;

clock U_clock(

.clk(clk),

.reset(reset),

.digit_sec(digit_sec),

.digit_min(digit_min)

);

UpCounter U_UpCounter(

.clk(clk),

.reset(reset),

.digit(digit)

);

fndController U_fndController(

.clk(clk),

.reset(reset),

.switch(switch),

.digit(digit),

.digit_sec(digit_sec),

.digit_min(digit_min),

.fndFont(fndFont),

.fndCom(fndCom)

);

endmodule

module clock(

input clk,

input reset,

output[5:0] digit_sec,

output[5:0] digit_min

);

wire w_clk_1s, w_clk_s;

clkDiv #(.MAX_COUNT(100_000_000)) U_ClkDiv_1s (

.clk (clk),

.reset(reset),

.o_clk(w_clk_1s)

);

counter #(.MAX_COUNT(60)) U_Counter_s (

.clk (w_clk_1s),

.reset(reset),

.count(digit_sec),

.o_min_clk(w_clk_s)

);

counter #(.MAX_COUNT(60)) U_Counter_m (

.clk (w_clk_s),

.reset(reset),

.count(digit_min)

);

endmodule

module UpCounter(

input clk,

input reset,

output[13:0] digit

);

wire w_clk_10hz;

wire [13:0] w_count_10k;

clkDiv #(.MAX_COUNT(100_000_000)) U_ClkDiv_1Hz(

.clk(clk),

.reset(reset),

.o_clk(w_clk_10hz)

);

counter #(.MAX_COUNT(10_000)) U_Counter_10k(

.clk(w_clk_10hz),

.reset(reset),

.count(digit)

);

endmodule

fndController.v

`timescale 1ns / 1ps

module fndController (

input clk,

input reset,

input switch,

input [13:0] digit,

input [5:0] digit_sec,

input [5:0] digit_min,

output [ 7:0] fndFont,

output [ 3:0] fndCom

);

wire [3:0] w_digit_1_clock, w_digit_10_clock, w_digit_100_clock, w_digit_1000_clock;

wire [3:0] w_digit_1_counter, w_digit_10_counter, w_digit_100_counter, w_digit_1000_counter;

wire [3:0] w_digit_clock, w_digit_counter, w_digit;

wire [1:0] w_count;

wire w_clk_1khz;

clkDiv #(.MAX_COUNT(100_000)) U_ClkDiv(

.clk(clk),

.reset(reset),

.o_clk(w_clk_1khz)

);

counter #(.MAX_COUNT(4)) U_Counter_2bit(

.clk(w_clk_1khz),

.reset(reset),

.count(w_count)

);

Decoder U_Decoder_2x4 (

.x(w_count),

.y(fndCom)

);

digitSplitter U_DigitSplitter (

.i_digit_sec(digit_sec),

.i_digit_min(digit_min),

.i_digit(digit),

.o_digit_1_clock(w_digit_1_clock),

.o_digit_10_clock(w_digit_10_clock),

.o_digit_100_clock(w_digit_100_clock),

.o_digit_1000_clock(w_digit_1000_clock),

.o_digit_1_counter(w_digit_1_counter),

.o_digit_10_counter(w_digit_10_counter),

.o_digit_100_counter(w_digit_100_counter),

.o_digit_1000_counter(w_digit_1000_counter)

);

Mux_4x1 U_Mux_clock (

.sel(w_count),

.x0 (w_digit_1_clock),

.x1 (w_digit_10_clock),

.x2 (w_digit_100_clock),

.x3 (w_digit_1000_clock),

.y (w_digit_clock)

);

Mux_4x1 U_Mux_counter (

.sel(w_count),

.x0 (w_digit_1_counter),

.x1 (w_digit_10_counter),

.x2 (w_digit_100_counter),

.x3 (w_digit_1000_counter),

.y (w_digit_counter)

);

Mux_2x1 U_Mux_2x1 (

.sel(switch),

.x0(w_digit_clock),

.x1(w_digit_counter),

.y(w_digit)

);

BCDtoSEG U_BcdToSeg (

.bcd(w_digit),

.seg(fndFont)

);

endmodule

module Decoder (

input [1:0] x,

output reg [3:0] y

);

always @(x) begin

case (x)

2'h0: y = 4'b1110;

2'h1: y = 4'b1101;

2'h2: y = 4'b1011;

2'h3: y = 4'b0111;

default: y = 4'b1110;

endcase

end

endmodule

module digitSplitter (

input [5:0] i_digit_sec,

input [5:0] i_digit_min,

input [13:0] i_digit,

output [ 3:0] o_digit_1_clock,

output [ 3:0] o_digit_10_clock,

output [ 3:0] o_digit_100_clock,

output [ 3:0] o_digit_1000_clock,

output [ 3:0] o_digit_1_counter,

output [ 3:0] o_digit_10_counter,

output [ 3:0] o_digit_100_counter,

output [ 3:0] o_digit_1000_counter

);

assign o_digit_1_clock = i_digit_sec % 10;

assign o_digit_10_clock = i_digit_sec / 10 % 10;

assign o_digit_100_clock = i_digit_min % 10;

assign o_digit_1000_clock = i_digit_min / 10 % 10;

assign o_digit_1_counter = i_digit % 10;

assign o_digit_10_counter = i_digit / 10 % 10;

assign o_digit_100_counter = i_digit / 100 % 10;

assign o_digit_1000_counter = i_digit / 1000 % 10;

endmodule

module Mux_4x1 (

input [1:0] sel,

input [3:0] x0,

input [3:0] x1,

input [3:0] x2,

input [3:0] x3,

output reg [3:0] y

);

always @(sel, x0, x1, x2, x3) begin

case (sel)

2'b00: y = x0;

2'b01: y = x1;

2'b10: y = x2;

2'b11: y = x3;

default: y = x0;

endcase

end

endmodule

module BCDtoSEG (

input [3:0] bcd,

output reg [7:0] seg

);

always @(bcd) begin

case (bcd)

4'h0: seg = 8'hc0;

4'h1: seg = 8'hf9;

4'h2: seg = 8'ha4;

4'h3: seg = 8'hb0;

4'h4: seg = 8'h99;

4'h5: seg = 8'h92;

4'h6: seg = 8'h82;

4'h7: seg = 8'hf8;

4'h8: seg = 8'h80;

4'h9: seg = 8'h90;

4'ha: seg = 8'h88;

4'hb: seg = 8'h83;

4'hc: seg = 8'hc6;

4'hd: seg = 8'ha1;

4'he: seg = 8'h86;

4'hf: seg = 8'h8e;

default: seg = 8'hff;

endcase

end

endmodule

module counter #(parameter MAX_COUNT = 4)(

input clk,

input reset,

output [$clog2(MAX_COUNT)-1:0] count,

output o_min_clk

);

reg [$clog2(MAX_COUNT)-1:0] counter = 0;

assign count = counter;

reg r_tick_1 = 0;

assign o_min_clk = r_tick_1;

always @(posedge clk, posedge reset) begin

if (reset == 1'b1) begin

counter <= 0;

end

else begin

if (counter == MAX_COUNT - 1) begin

counter <= 0;

r_tick_1 <= 1'b1;

end

else begin

counter <= counter + 1;

r_tick_1 <= 1'b0;

end

end

end

endmodule

module clkDiv #(parameter MAX_COUNT = 100)(

input clk,

input reset,

output o_clk

);

reg [$clog2(MAX_COUNT)-1:0] counter = 0;

reg r_tick = 0 ;

assign o_clk = r_tick;

always @(posedge clk, posedge reset) begin

if (reset) begin

counter <= 0;

end

else begin

if (counter == (MAX_COUNT - 1)) begin

counter <= 0;

r_tick <= 1'b1;

end

else begin

counter <= counter + 1;

r_tick <= 1'b0;

end

end

end

endmodule

module Mux_2x1 (

input sel,

input [3:0]x0,

input [3:0]x1,

output reg [3:0] y

);

always @(sel, x0, x1) begin

case (sel)

1'b0: y = x0;

1'b1: y = x1;

default: y = x0;

endcase

end

endmodule

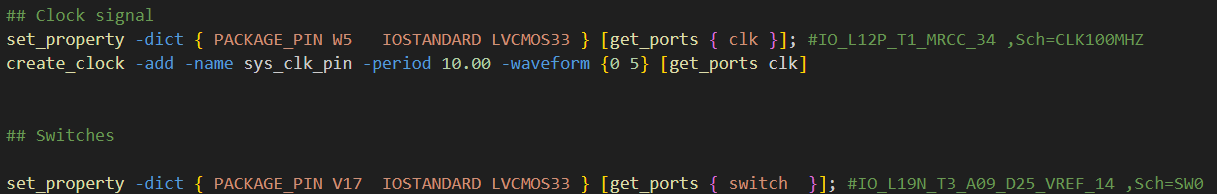

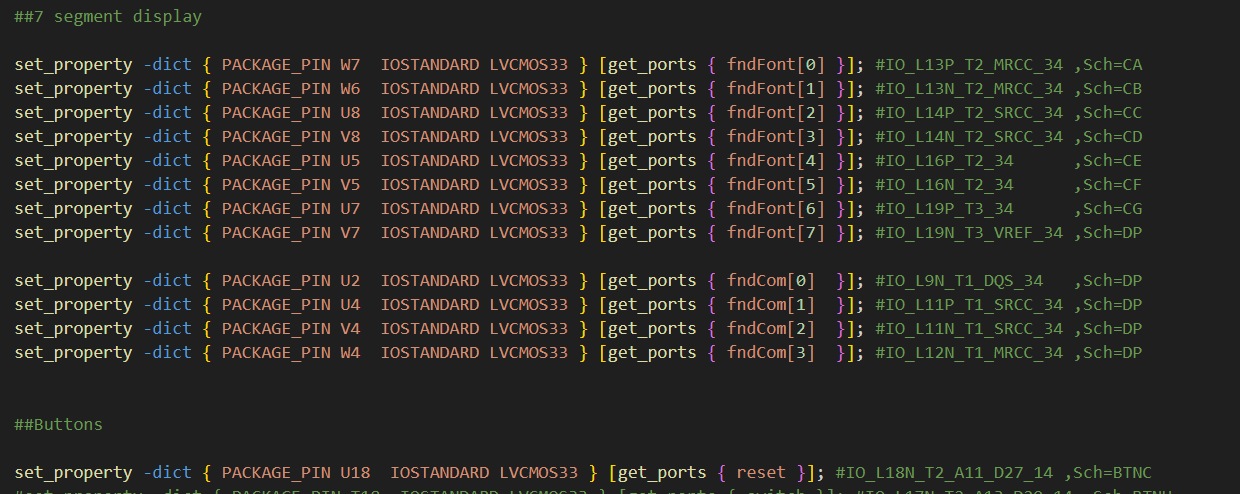

simulation

constraint

video

'[하만]세미콘 아카데미 > verilog' 카테고리의 다른 글

| 0514 upCounter_Fnd_moore_machine | 2024.06.22 |

|---|---|

| 0514 assignment, FSM, button_moore_mealy | 2024.06.22 |

| 0510 clockCounter, upCounter | 2024.06.22 |

| 0510_8bitAdder_display | 2024.06.22 |

| 0509 4bit_Full_Adder & FND 표시 | 2024.06.22 |